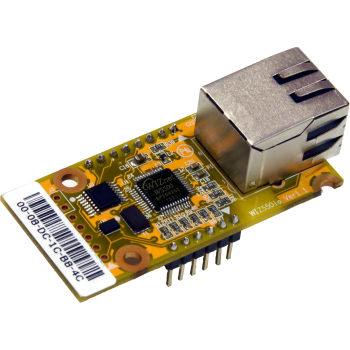

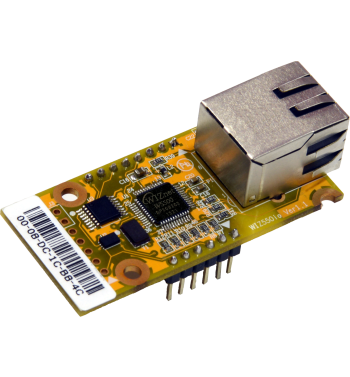

W5500

Delivery Time: 7 days for quantities in stock. Backordered pieces: 4 weeks

Description

The W5500 chip is a Hardwired Internet controller designed as a full hardwired TCP/IP stack with WIZnet technology. W5500 provides Internet connectivity to your embedded systems by using SPI(Serial Peripheral Interface). SPI provides easy connection via external MCU to W5500. The clock speed of W5500 SPI supports upto 80MHz.

Since W5500 integrates the Hardwired TCP/IP stack with 10/100 Ethernet MAC and PHY, it is truly a one-chip solution for the stable internet connectivity. WIZnet's Hardwired TCP/IP stack supports TCP, UDP, IPv4, ICMP, ARP, IGMP, and PPPoE - and it has been proven through various applications over the last decade.

Features

- Supports following Hardwired TCP/IP Protocols : TCP, UDP, ICMP, IPv4, ARP, IGMP, PPPoE

- Supports 8 independent sockets simultaneously

- Supports Power down mode

- Supports Wake on LAN over UDP

- Supports High Speed Serial Peripheral Interface(SPI MODE 0, 3)

- Internal 32Kbytes Memory for Tx/Rx Buffers

- 10BaseT/100BaseTX Ethernet PHY embedded

- Support Auto Negotiation (Full and half duplex, 10 and 100-based)

- Not support IP Fragmentation

- 3.3V operation with 5V I/O signal tolerance

- LED outputs (Full/Half duplex, Link, Speed, Active)

- 48 Pin LQFP Lead-Free Package (7x7mm, 0.5mm pitch)

Related Links

| Manufacturer / Hersteller | WIZnet Korea |

|---|---|

| Dimension | 7 mm x 7 mm |

| Ethernet I/F | PHY |

| Operating Temperature | -40 °C to +85 °C |

| Operating Voltage | 3.3 V |

| Functions | 3-in-1, TCP/IP + MAC + PHY |

| Network sockets count | 8 |

| internal DPRAM buffer memory | 32 kB |

| Package | QFN |

| pin count chip | 64 |

| MCU I/F | SPI |

| pin pitch | 0.50 mm |

| Ethernet Speed | 10/100 |

| Protocol | IPv4 |

| Auto Negotiation | Yes |

| Wake on Lan | Yes |

| Power Down Mode | Yes |

| MCU core | ARM Cortex M0 |

| Core speed | 96 MHz |